分類:ハーネスアセンブリ

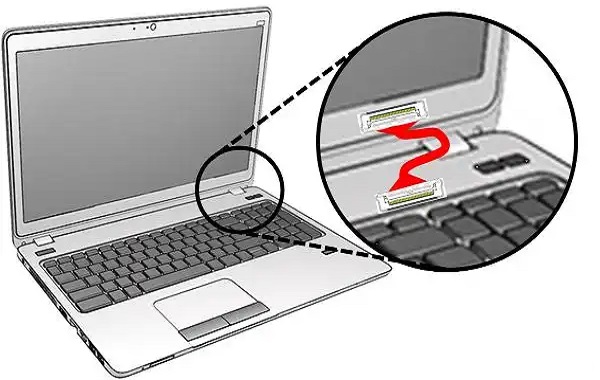

一、eDP高帯域幅モードと接続の課題

eDPはDisplayPortアーキテクチャに基づいており、多チャネルデジタル差分信号を通じて高速なビデオデータ転送を実現しています。その帯域幅レベルはHBR(2.7Gbps/チャネル)からHBR2(5.4Gbps/チャネル)およびHBR3(8.1Gbps/チャネル)に向上し、8Kおよび没入感のあるディスプレイの要求を満たすHBR4に進化しています。帯域幅の向上により、インサー损失、反射、交叉干渉およびEMIの問題が顕著に拡大し、伝統的な排線方案が性能の限界に近づいており、束ねられたケーブルの構造設計および電気的性能に対するより高い要求が提出されています。

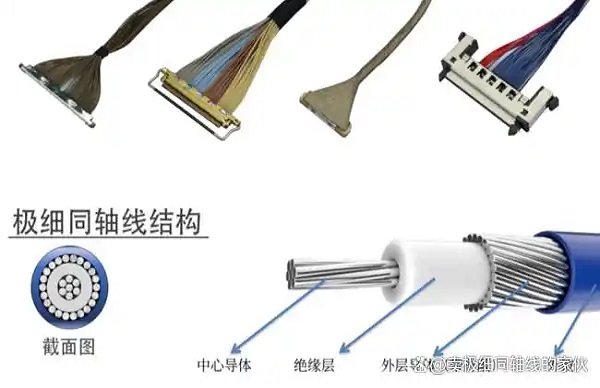

二、極細同軸線束在高速表示における利点

極細同軸線束は同心導体と全体屏蔽構造を用い、安定した特性抵抗と優れた屏蔽効果を持ち、HBR3以上の高速モードで信号の減衰と干渉を効果的に低減することができます。その線径が細かく、柔軟性に優れ、超薄型全体、高密度配線、折り曲げ、軸受など複雑な構造の応用場面に適しています。また、同軸屏蔽構造は電磁放射と外の干渉を低減し、システムの電磁適合性と長期信頼性を向上させます。

三、HBR3とHBR4向けの配線設計ポイント

高帯域幅eDPアプリケーションにおいて、線束設計では阻抗一致性、線長と損耗の制御、およびシールドと接地方法の適切性に特に注意を払う必要があります。不適合や過大な損耗により信号の品質が低下することを避けるためにです。コネクタ端子の構造設計、コート工法、および組み立て精度も、全体の伝送性能に直接的な影響を与えます。実際のアプリケーションでは、眼図分析、誤码率テスト、およびシステムレベルの確認を通じて、線束が全速走行条件で安定するように確保することが、信頼性の高い大量生産を実現する重要な要素です。